# Multicore Workshop

Cache Coherency

Mark Bull David Henty

EPCC, University of Edinburgh

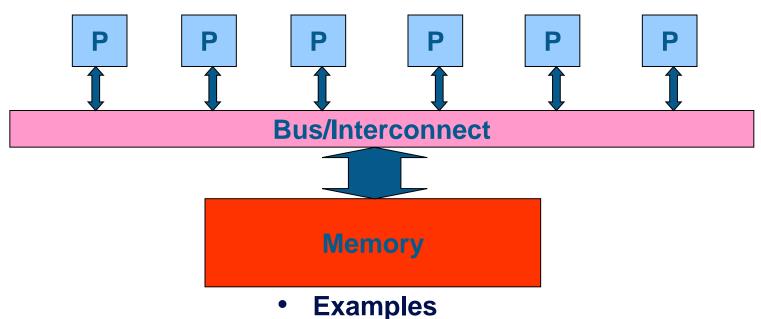

## Symmetric MultiProcessing

- Each processor in an SMP has equal access to all parts of memory

- same latency and bandwidth

- IBM servers, Sun HPC Servers, Fujitsu PrimePower, multiprocessor PCs

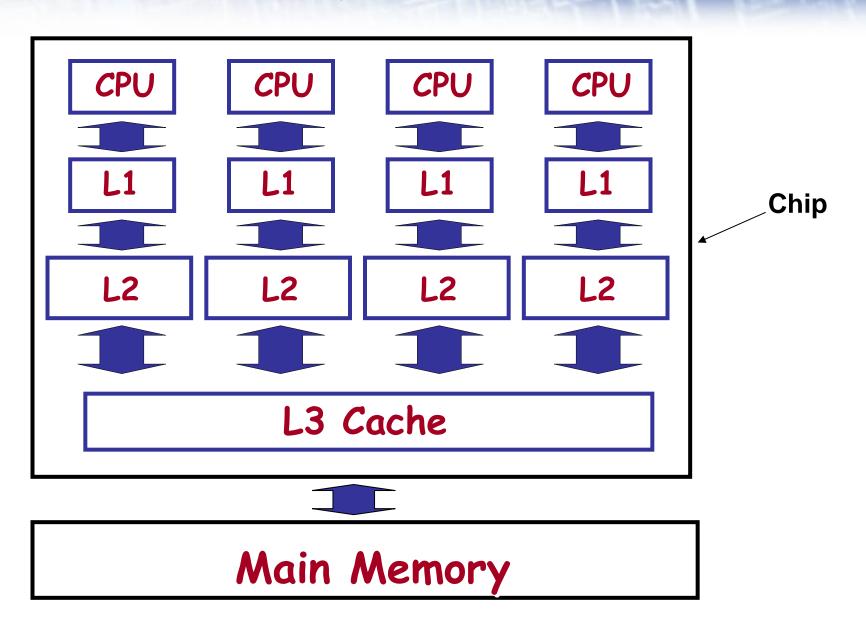

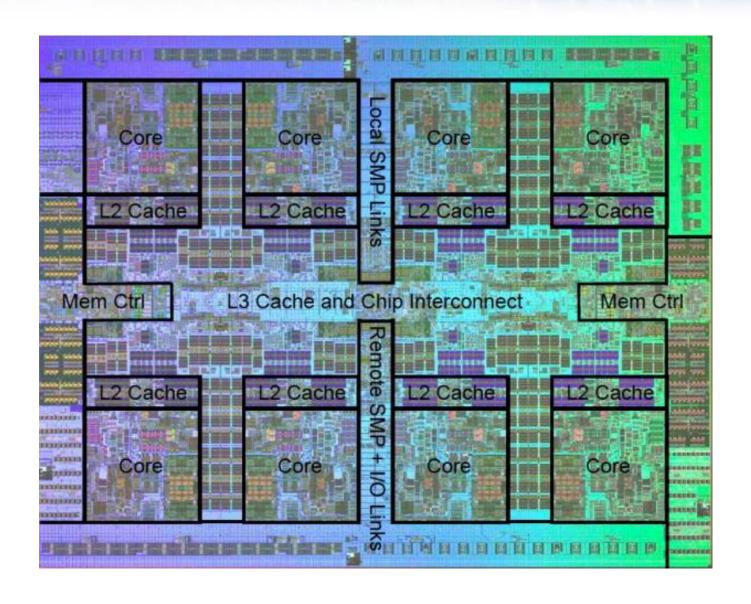

#### Multicore chips

- Now possible (and economically desirable) to place multiple processors on a chip.

- From a programming perspective, this is largely irrelevant

- simply a convenient way to build a small SMP

- on-chip buses can have very high bandwidth

- Main difference is that processors may share caches

- Typically, each core has its own Level 1 and Level 2 caches, but the Level 3 cache is shared between cores

### Typical cache hierarchy

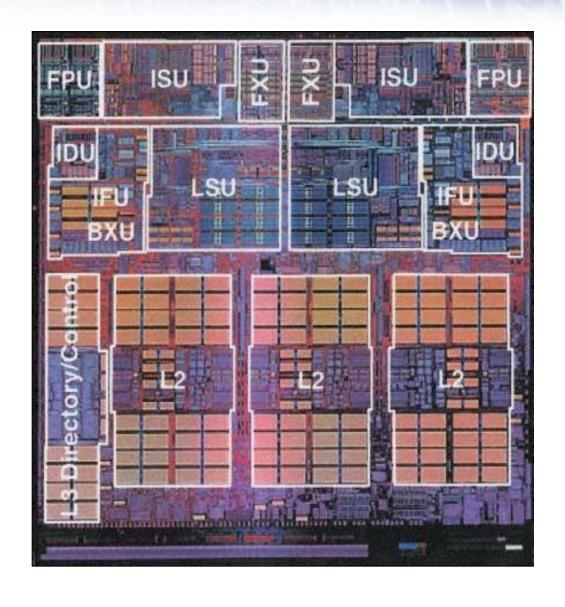

## Power4 two-core chip

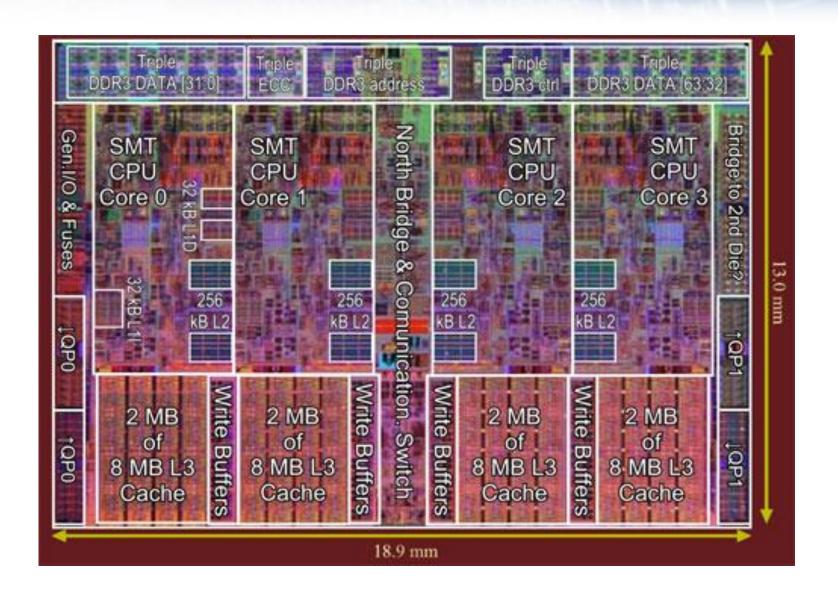

#### Intel Nehalem quad-core chip

#### Power7 8-core chip

- This means that multiple cores on the same chip can communicate with low latency and high bandwidth

- via reads and writes which are cached in the shared cache

- However, cores contend for space in the shared cache

- one thread may suffer capacity and/or conflict misses caused by threads/processes on another core

- harder to have precise control over what data is in the cache

- if only single core is running, then it may have access to the whole shared cache

- Cores also have to share off-chip bandwidth

- for access to main memory

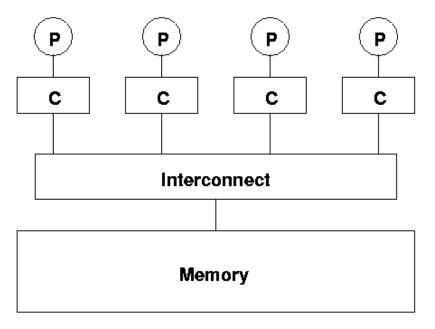

#### Multiprocessors

Simple way to build a (small-scale) parallel machine is to connect multiple processors to a single memory (true shared memory)

Shared memory

#### Cache coherency

- Main difficulty in building multiprocessor systems is the cache coherency problem.

- The shared memory programming model assumes that a shared variable has a unique value at a given time.

- Caching in a shared memory system means that multiple copies of a memory location may exist in the hardware.

- To avoid two processors caching different values of the same memory location, caches must be kept coherent.

- To achieve this, a write to a memory location must cause all other copies of this location to be removed from the caches they are in.

#### Coherence protocols

- Need to store information about sharing status of cache blocks

- has this block been modified?

- is this block stored in more than one cache?

- Two main types of protocol

- 1. Snooping (or broadcast) based

- every cached copy caries sharing status

- no central status

- all processors can see every request

- 2. Directory based

- sharing status stored centrally (in a directory)

#### Snoopy protocols

- Already have a valid tag on cache lines: this can be used for invalidation.

- Need an extra tag to indicate sharing status.

- can use clean/dirty bit in write-back caches

- All processors monitor all bus transactions

- if an invalidation message is on the bus, check to see if the block is cached, and if so invalidate it

- if a memory read request is on the bus, check to see if the block is cached, and if so return data and cancel memory request.

- Many different possible implementations

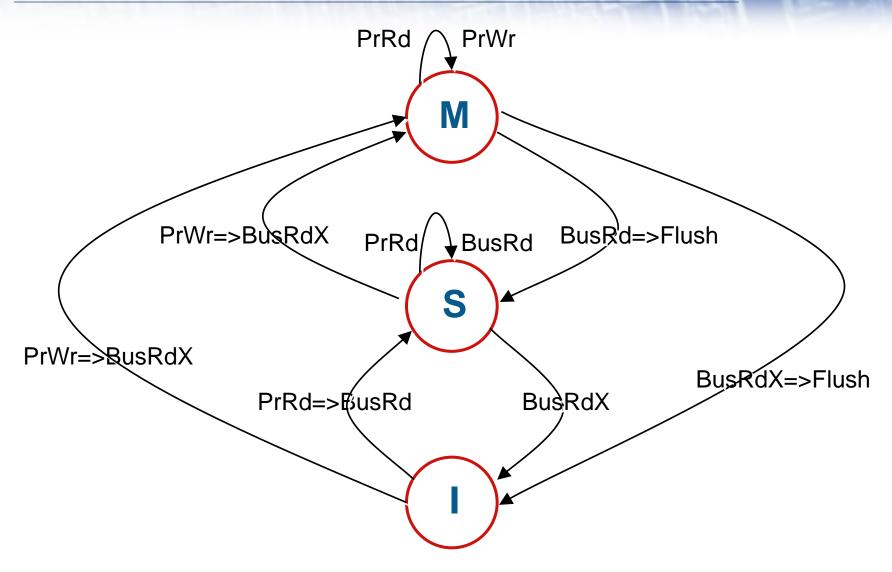

#### 3 state snoopy protocol: MSI

- Simplest protocol which allows multiple copies to exist

- Each cache block can exist in one of three states:

- <u>M</u>odified: this is the only valid copy in any cache and its value is different from that in memory

- Shared: this is a valid copy, but other caches may also contain it, and its value is the same as in memory

- *Invalid*: this copy is out of date and cannot be used.

- Model can be described by a state transition diagram.

- state transitions can occur due to actions by the processor, or by the bus.

- state transitions may trigger actions

#### **Processor actions**

- read (PrRd)

- write (PrWr)

#### **Bus actions**

- read (BusRd)

- read exclusive (BusRdX)

- flush to memory (Flush)

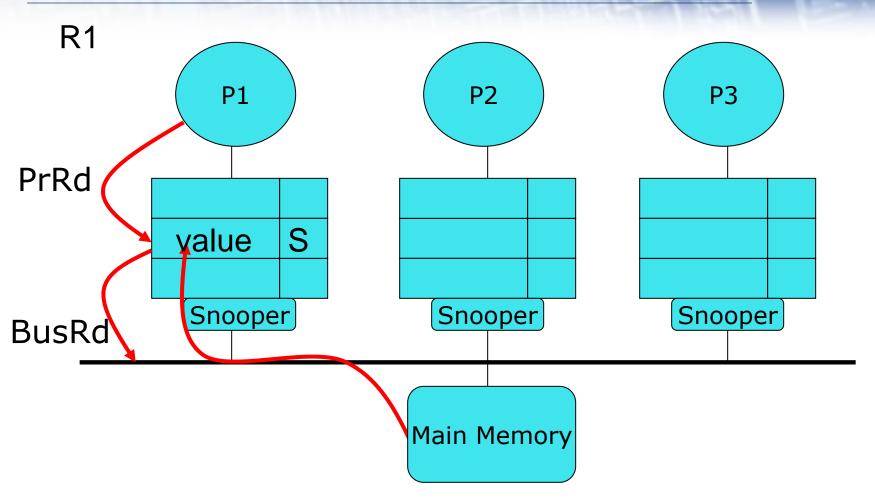

#### MSI Protocol walk through

- Assume we have three processors.

- Each is reading/writing the same value from memory where R1 means a read by processor 1 and W3 means a write by processor 3.

- For simplicity sake, the memory location will be referred to as "value."

- The memory access stream we will walk through is:

R1, R2, W3, R2, W1, W2, R3, R2

P1 wants to read the value. The cache does not have it and generates a BusRd for the data. Main memory controller provides the data. The data goes into the cache in the shared state.

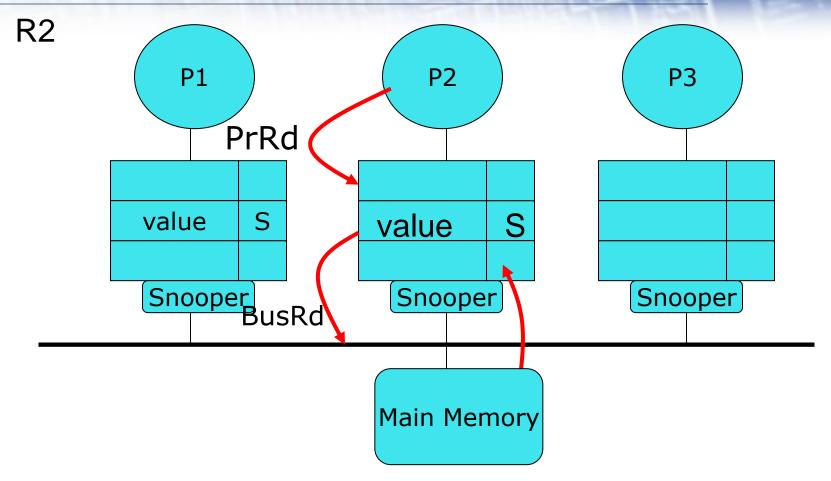

P2 wants to read the value. Its cache does not have the data, so it places a BusRd to notify other processors and ask for the data. The memory controller provides the data.

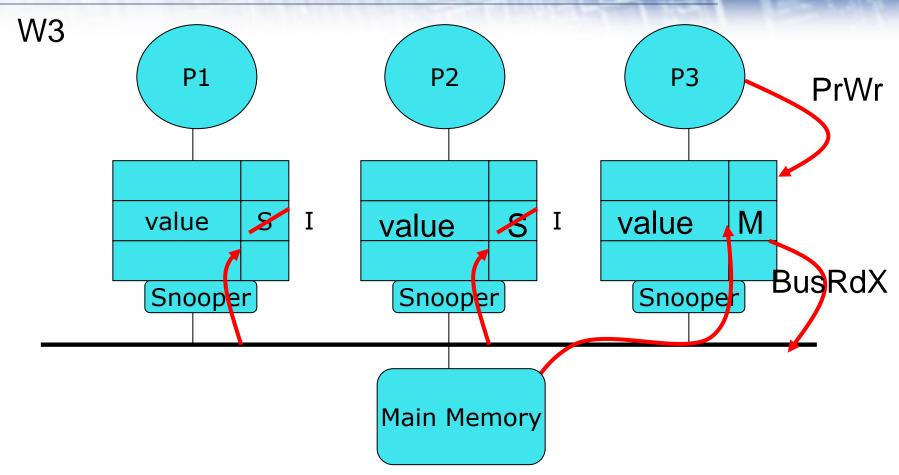

P3 wants to write the value. It places a BusRdX to get exclusive access and the most recent copy of the data. The caches of P1 and P2 see the BusRdX and invalidate their copies. Because the value is still up-to-date in memory, memory provides the data.

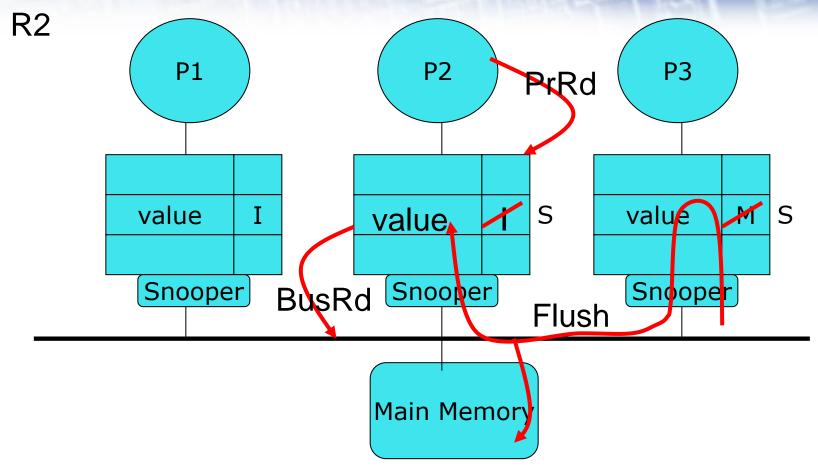

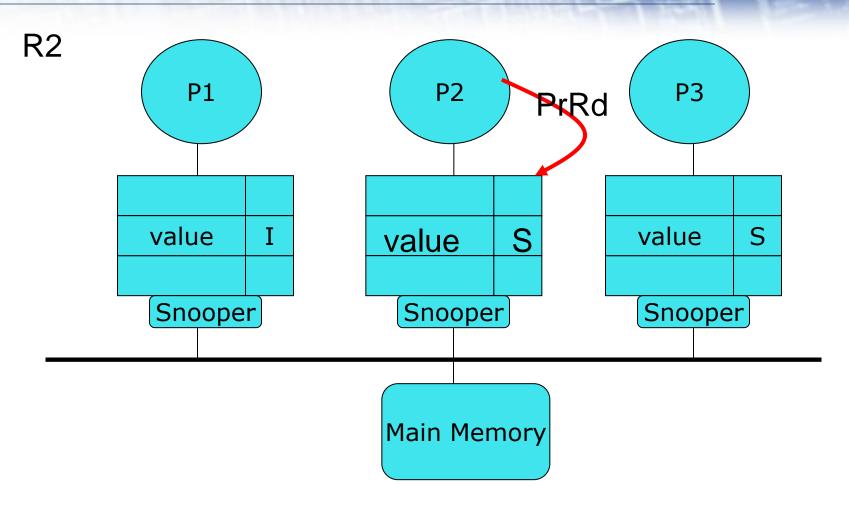

P2 wants to read the value. P3's cache has the most up-to-date copy and will provide it. P2's cache puts a BusRd on the bus. P3's cache snoops this and cancels the memory access because it will provide the data. P3's cache flushes the data to the bus.

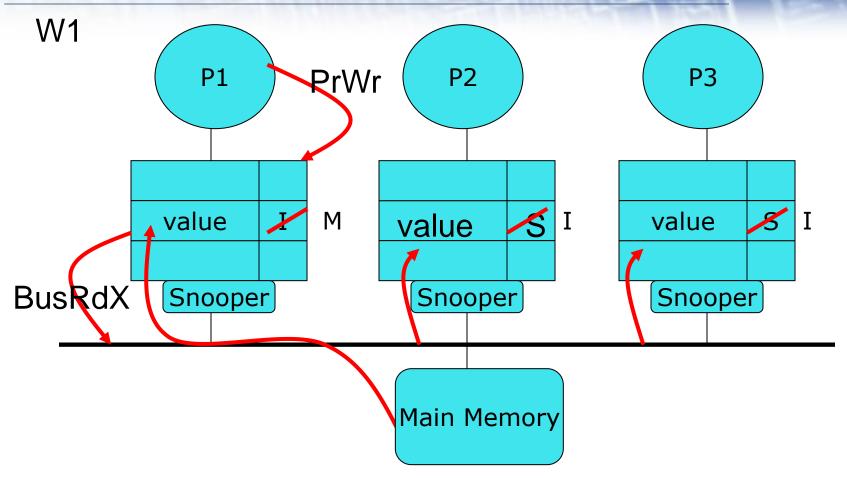

P1 wants to write to its cache. The cache places a BusRdX on the bus to gain exclusive access and the most up-to-date value. Main memory is not stale so it provides the data. The snoopers for P2 and P3 see the BusRdX and invalidate their copies in cache.

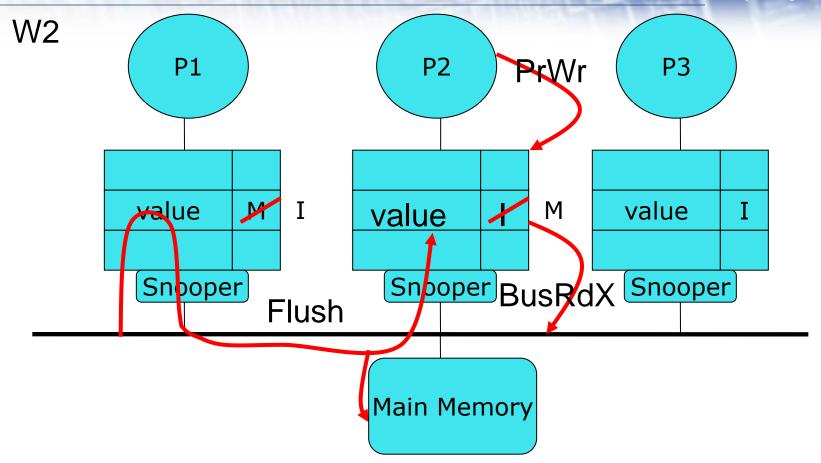

P2 wants to write the value. Its cache places a BusRdX to get exclusive access and the most recent copy of the data. P1's snooper sees the BusRdX and flushes the data to the bus. Also, it invalides the data in its cache and cancels the memory access.

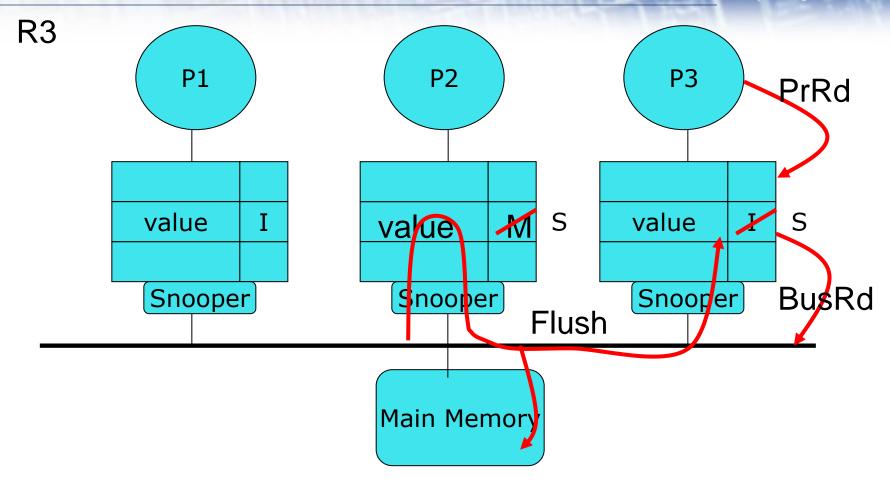

P3 wants to read the value. Its cache does not have a valid copy, so it places a BusRd on the bus. P2 has a modified copy, so it flushes the data on the bus and changes the status of the cache data to shared. The flush cancels the memory access and updates the data in memory as well.

P2 wants to read the value. Its cache has an up-to-date copy. No bus transactions need to take place as there is no cache miss.

#### MSI state transitions

A=>B means that when action A occurs, the state transition indicated happens, and action B is generated

#### Other protocols

- MSI is inefficient: it generates more bus traffic than is necessary

- Can be improved by adding other states, e.g.

- <u>Exclusive</u>: this copy has not been modified, but it is the only copy in any cache

- <u>Owned</u>: this copy has been modified, but there may be other copies in shared state

- MESI and MOESI protocols are more commonly used protocols than MSI

- MSI is nevertheless a useful mental model for the programmer

- Also possible to update values in other caches on writes, instead of invalidating them

#### False sharing

- The units of data on which coherency operations are performed are cache blocks: the size of these units is usually 64 or 128 bytes.

- The fact that coherency units consist of multiple words of data gives rise to the phenomenon of false sharing.

- Consider what happens when two processors are both writing to different words on the same cache line.

- no data values are actually being shared by the processors

- Each write will invalidate the copy in the other processor's cache, causing a lot of bus traffic and memory accesses.

- same problem if one processor is writing and the other reading

- Can be a significant performance problem in threaded programs

- Quite difficult to detect